## Stress phenomena in times of porous low-k dielectrics

O. Aubel, M. Grillberger, J. Poppe, M. Lehr, C. Hennesthal

11<sup>th</sup> international workshop on stress-induced phenomena in metallization

- Why are we moving to ultra-lower-k (ULK) materials?

- What are the general challenges with ULK?

- What are the challenges for reliability?

- What are improvement options in particular for Stress migration?

- Summary

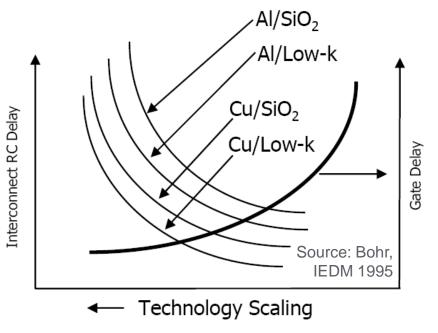

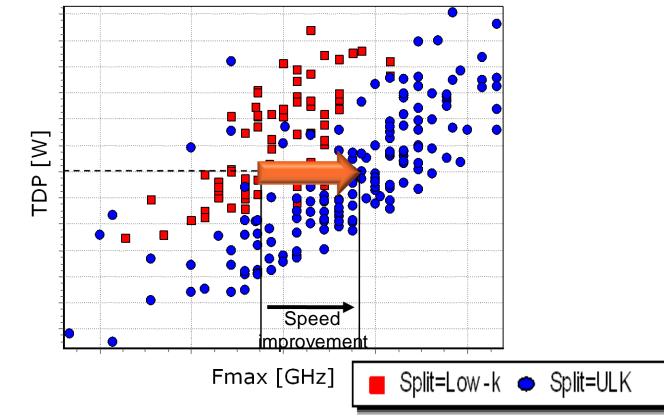

- In advanced technologies not only the transistor is limiting the overall performance anymore

- RC delays are more and more limiting the speed of the system

### Why are we moving to ULK materials?

- How to reduce RC?

- Limited ways to reduce resistance [thinner barrier and/or deeper trench]

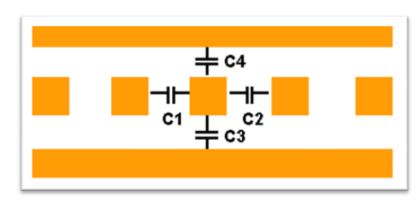

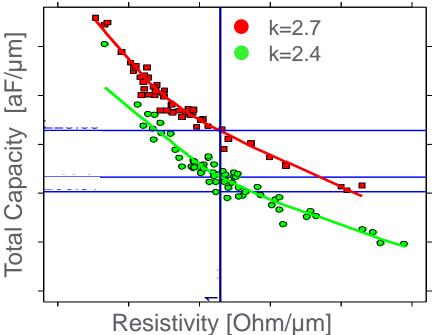

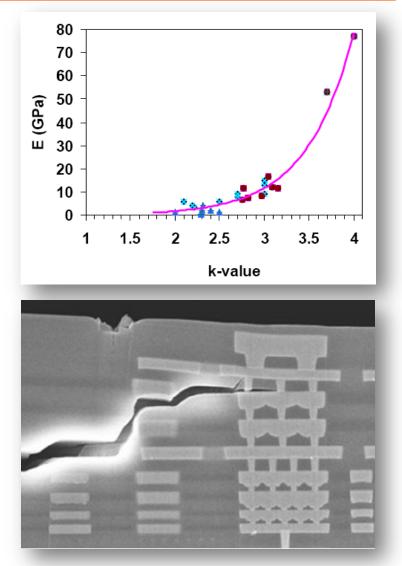

- Ultra Low K (ULK) materials are films with a bulk k-value of <2.6.</li>

Between k-values of 2.6 and 3 the ILD is considered a low K (LK) material

- Up-to-date ILDs have k-values of ~2.7, a RC reduction of >10% can be reached by moving to a material with k=2.4 or below

- Does ULK work in integrated circuits?

- Yes, several 100MHz speed improvement for the same IC can be achieved (non-design optimized)

#### What are the general challenges with ULK?

### What are the general challenges with ULK?

- ULK is a porous material which is mechanically weaker than dense ILDs (and therefore more prone to cracks due to packaging)

- ULK must be integrated using different UNIT processes

- ULK is more sensitive to process damages

- ULK is intrinsically less robust with respect to reliability

- Moisture uptake increases the risk of barrier oxidation

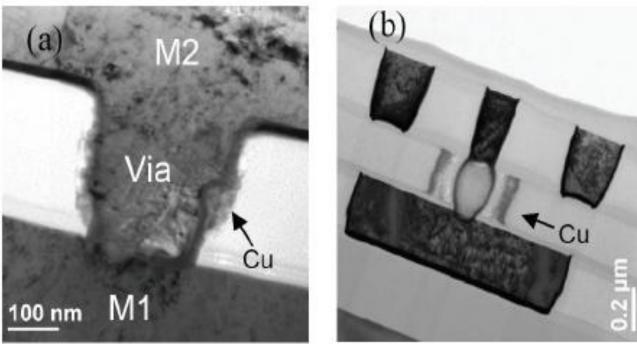

- Cu out-diffusion through the barrier was observed resulting in a significant TDDB lifetime decrease

Source: Baek, et al., IRPS, 2006

Source: Michael, et al., APL 83, 2003

What are the general challenges with ULK?

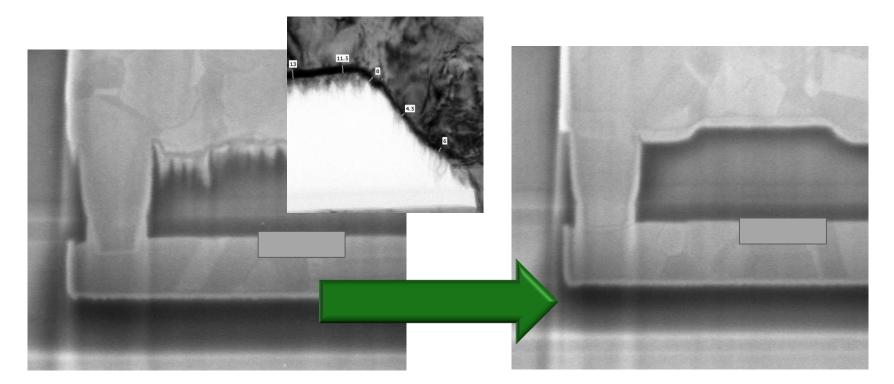

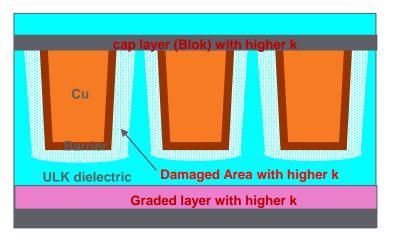

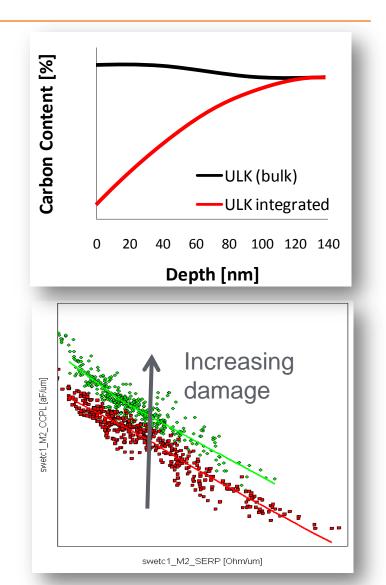

- The ULK is very prone to severe damage due to liner processing

- Only smooth etch back processes allow reliable ULK integration

- Integration of ULK is very challenging:

- The Etch process is introducing a damage region which increases the effective k-value of the film

- Damage region is not scaling and will become more and more significant in future

- ULK damage

- due to liner processes  $\rightarrow$  bad reliability and RC values

- due to etch damage  $\rightarrow$  bad reliability and RC values

- Moisture uptake → barrier oxidation (and bad TDDB)

- Cracks or delamination due to packaging

### What are the challenges for reliability?

What are the challenges for reliability (EM)? Intrinsic Reliability Impact!

- Different liner schemes for reduced damage in particular on trench bottom needed

- Comparable EM performance can be reached for ULK compared to dense low-K (k=2.7)

- EM kinetics are comparable

- For Cu silicidation the E<sub>A</sub> value is ~1.0eV

- For pure Cu the E<sub>A</sub> value is ~ 0.9eV

Intrinsic EM reliability robustness is not affected by ULK introduction

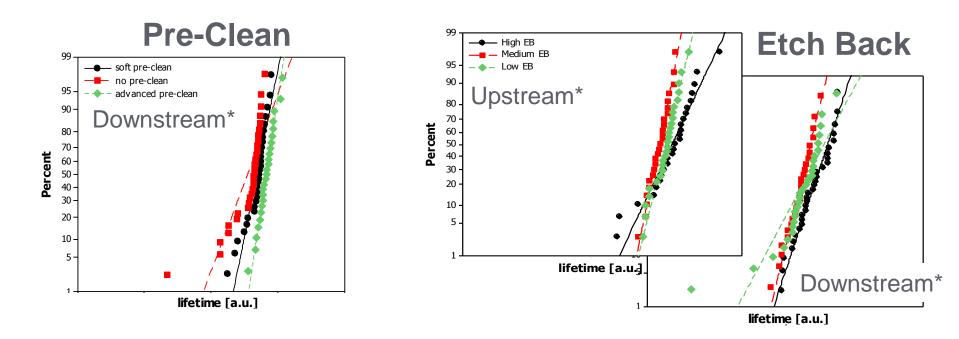

What are the challenges for reliability (EM)? Process Impact on Reliability!

Significant impact on EM was observed by pre-clean splits after via etch and the barrier schemes (etch back).

#### Optimized integration schemes eliminate any process related impact on EM

\*Line width~140nm

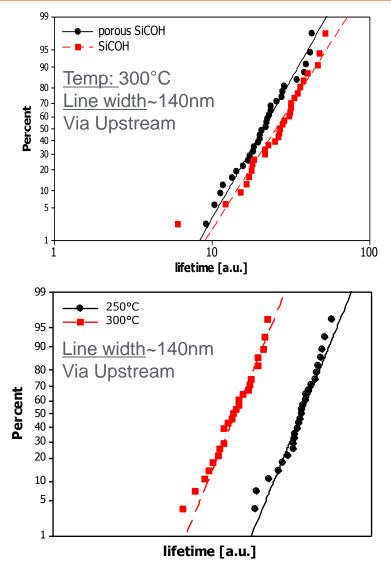

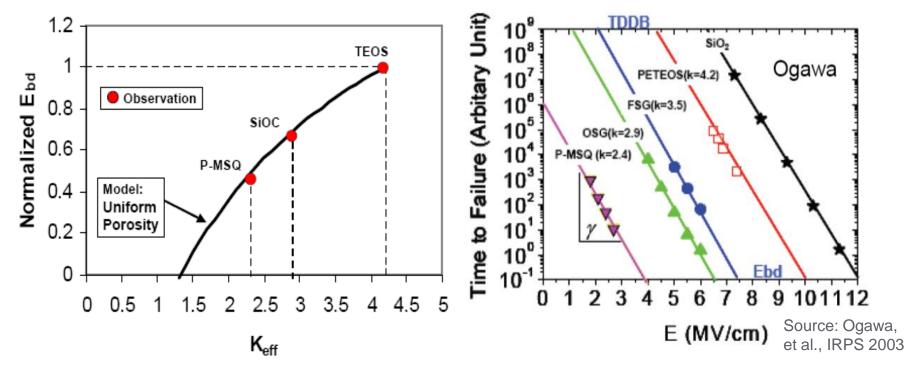

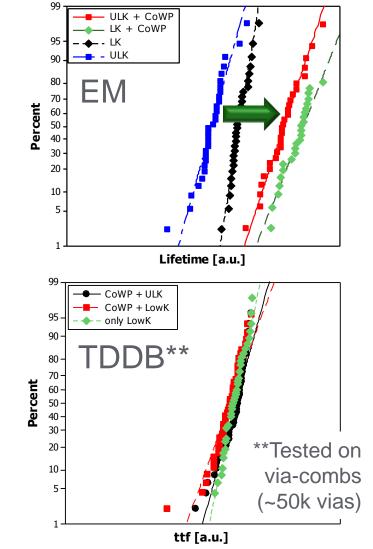

What are the challenges for reliability (TDDB)? Intrinsic Reliability Impact!

Porous materials have about 30% less breakdown strength than dense materials

#### Intrinsic TDDB reliability suffers from ULK introduction

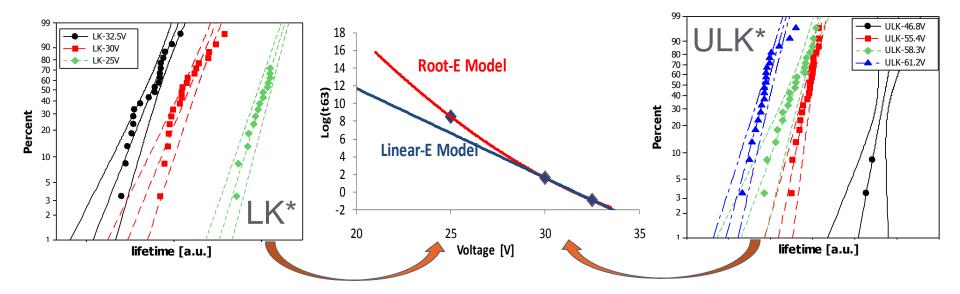

What are the challenges for reliability (TDDB)? Intrinsic Reliability Impact!

IMD-TDDB measurements are indicating that the physical mechanisms are not changing between the different ILDs

TDDB lifetime extrapolation stays the same (root-E model valid for ULK)

\*Tested on via-combs (~50k vias)

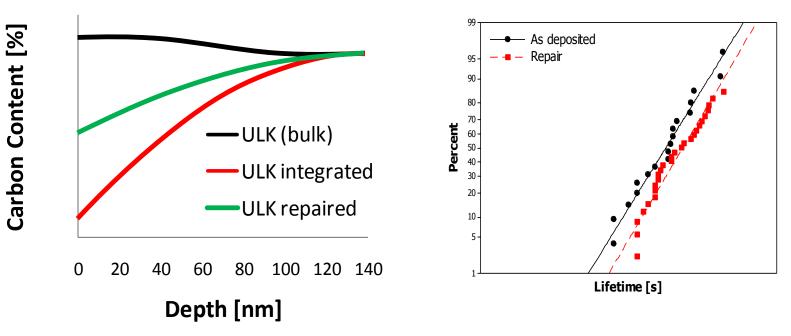

What are the challenges for reliability (TDDB)? Process Impact on Reliability!

- Two ways to improve TDDB performance

- Avoid damage (ACP)

- Repair damage (ULK repair)

- Both are improving lifetime and V<sub>acc</sub>

Optimized integration schemes reduce process related impact on TDDB

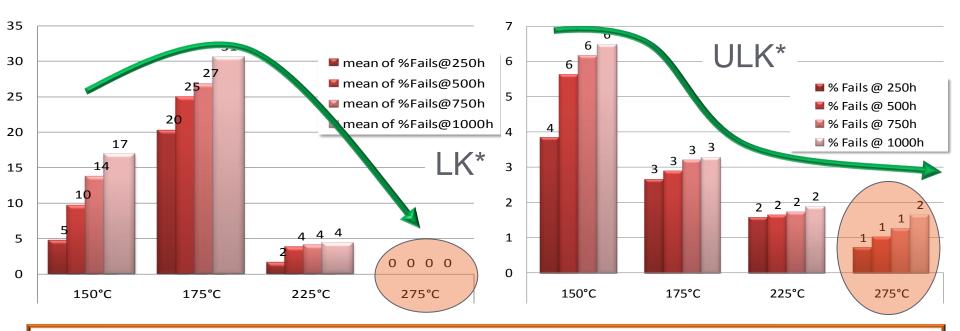

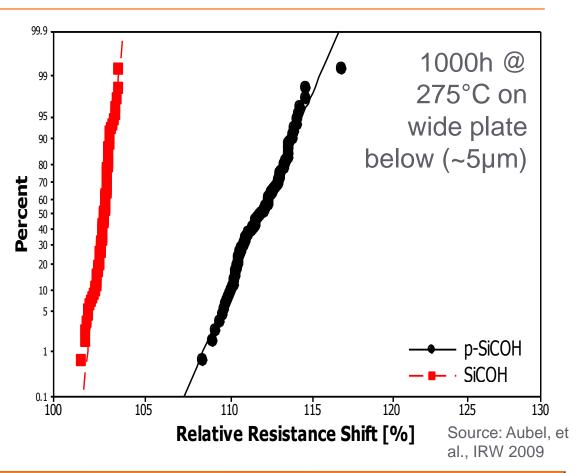

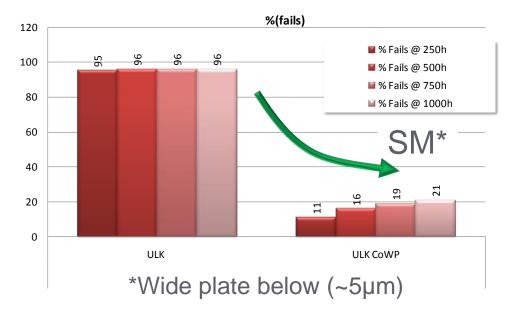

What are the challenges for reliability (SM)? Intrinsic Reliability Impact!

- SM peak temperature seem to move to 150°C

- High temperature behavior has changed

Intrinsic SM reliability behavior may change due to ULK introduction

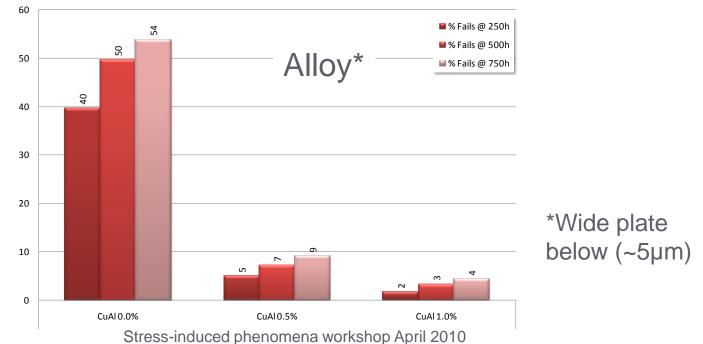

\*Wide plate below (~5µm)

What are the challenges for reliability (SM)? Intrinsic Reliability Impact!

- Since ULK is porous and therefore much more sensitive to oxygen diffusion

- The barrier oxidation (BIT) is much more pronounced compared to LK

Intrinsic high temperature SM behavior changes due to ULK introduction

What are the challenges for reliability (SM)? Intrinsic Reliability Impact!

- Intrinsic SM reliability physics may change due to ULK introduction

- "peak" SM temperature seems to decrease down to 150°C or below

- High temperature behavior (Barrier Integrity)

- Possible root causes:

- Low temperature:

- ULK deposition temperature is well below the deposition temperature from LK, but measured stress (as deposited) = 45GPa is identical to LK

- CTE<sub>ULK</sub> is 14ppm/K compared to CTE<sub>LK</sub> is 11ppm/K

- High temperature:

- Moisture sensitivity, higher diffusivity for oxygen, ULK serving as oxygen source

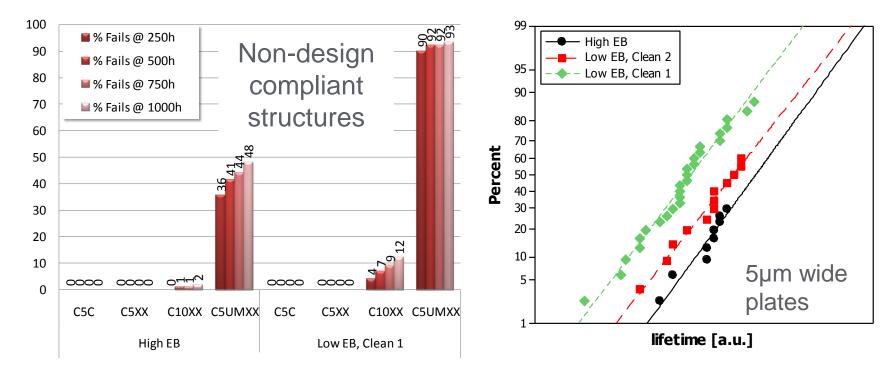

What are the challenges for reliability (SM)? Process Impact on Reliability!

#### SM is very sensitive to barrier schemes

- comparable to EM: smooth barrier has reduces SM margin but can be compensated by pre-clean processes

- Still some margin for meeting targets

### What are the challenges for reliability (Status)?

| Mechanism | Comment                                                                                                                                                                                                                                                                                            | Status |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| EM        | <ul> <li>No impact on intrinsic EM reliability<br/>robustness</li> <li>LK Performance can be met by optimized<br/>process (not process impact on EM<br/>performance)</li> </ul>                                                                                                                    |        |

| TDDB      | <ul> <li>Very critical due to "intrinsic" material degradation (lower V<sub>acc</sub> and lower V<sub>BD</sub>)</li> <li>No change in extrapolation methodology observed</li> <li>Lifetime margin is reduced compared to LK</li> <li>Process impact can be reduced by optimized process</li> </ul> |        |

| SM        | <ul> <li>Intrinsic SM reliability behavior changes<br/>due to ULK introduction</li> <li>Peak stress temperature is changing</li> <li>Barrier integrity performance is challenging</li> </ul>                                                                                                       |        |

## What are improvement options in particular for Stress migration?

## Using the toolbox of EM enhancement options

- 1. CoWP cap layer

- Max. EM improvement

- Max. SM improvement

- TDDB challenging

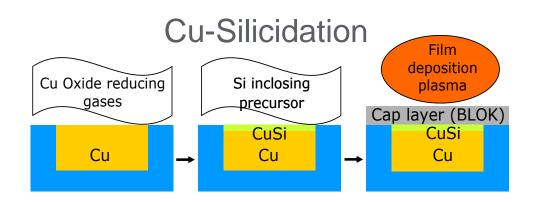

- 2. Cu-Silicidation

- Some EM improvement

- Some SM improvement

- TDDB improvement

- RC challenging

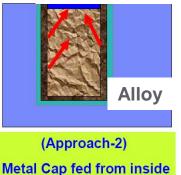

- 3. Alloy

- Some EM improvement

- Some SM improvement

- RC challenging

CuMn Seed Layer

# How to solve these problems in SM? $\rightarrow$ CoWP on ULK

- During early process development CoWP was investigated for EM/SM improvements and TDDB impact

- EM and SM improvement is significant (for EM >> t50 improvement)

- No impact on TDDB has been observed

Stress-induced phenomena workshop April 2010

How to solve these problems in SM?  $\rightarrow$  Alloy and Silicidation

- The electromigration enhancement options work for stress migration accordingly

- Cu seed alloy with e.g. Al significantly improves SM performance for wide plates (>5µm)

- Cu surface silicidation significantly reduces stress migration failures in wide plates

#### Summary and Conclusions

- The introduction of porous ULK material is very challenging for the integration as well as for the reliability

- Barrier seed depositions techniques will need to be reevaluated to reduced the damage for the underlying ILD

- Electromigration in down flow direction is suffering from the adopted barrier –seed process but can be adjusted by advanced pre-clean processes

- TDDB is significantly degraded due to the change of material properties as well as the ULK damage of the process. ULK repair techniques can help to reduce the process influence.

- The physics of stress migration behavior seem to change with respect to high temperature and <u>low temperature regime which can be compensated</u> <u>by EM enhancement options</u>.

### The authors like to thank:

Frank Feustel, Carsten Peters, Holger Schuehrer, Jens Hahn and Meike Hauschildt (all with Globalfoundries Fab 1 in Dresden) and our colleagues in Sunnyvale (Ca, USA) Kok-Yong Yiang, Walter Yao and Patrick Justison for helpful discussions.

#### **Trademark Attribution**

GLOBALFOUNDRIES, the GLOBALFOUNDRIES logo and combinations thereof are trademarks of GLOBALFOUNDRIES Inc. in the United States and/or other jurisdictions. Other names used in this presentation are for identification purposes only and may be trademarks of their respective owners.

©2009 GLOBALFOUNDRIES Inc. All rights reserved.